https://tinyurl.com/ucrtrm3

這篇文章有示意圖

https://images.anandtech.com/doci/15219/17.92%20wafer.png

這個是八成的晶圓

可以看到每個晶片都很小

只有 17.92 mm^2

如果把那些failed 的晶片想成defect

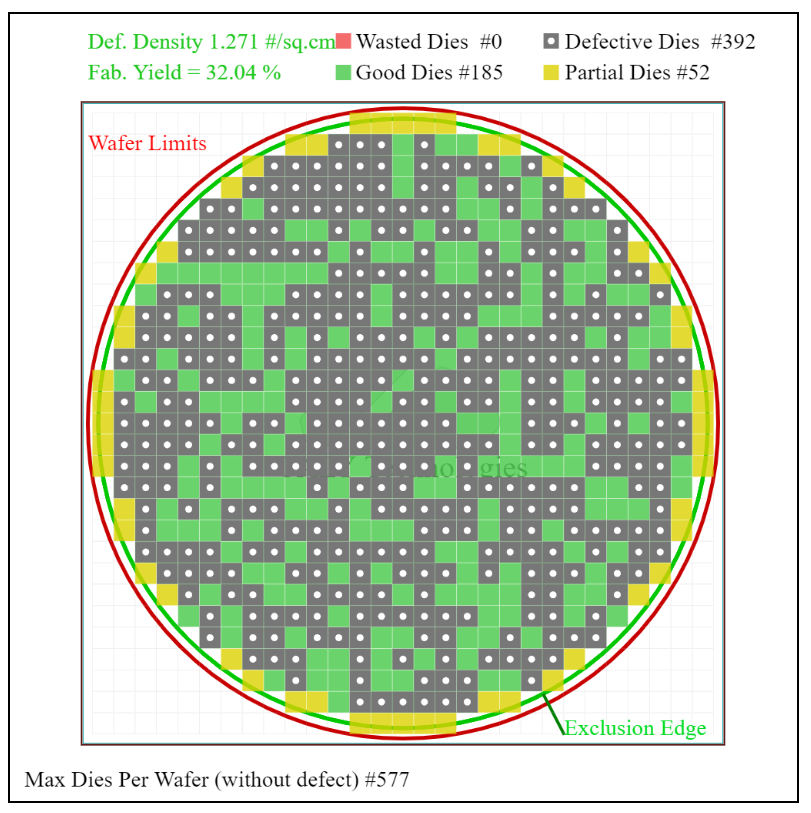

然後現在把晶片放大六倍

到100 mm^2 (相當於蘋果處理器的大小)

只要晶片有包含那個defect就算失敗的話

那良率就變成這樣:

https://images.anandtech.com/doci/15219/100%20wafer.png

良率直接從8成掉到32%

所以以這個良率來看要生產還是不太行的

※ 引述《dragonjj (簡簡單單的傷過 就不算白)》之銘言:

: -------------------------------發文提醒----------------------------------

: 1.發文前請先詳閱[新聞]分類發文規範,未依規範發文將受處份。

: 2.連結過長請善用 https://goo.gl/ 縮網址,連結能不能點擊者板規1-2-2處份。

: 3.心得/評論請盡量充實,心得過短或濫竽充數將會以1-2-3&一行文規範水桶處份。

: ---------------------------按ctrl+y可刪除以上內容。----------------------

: 1.原文連結:

: ※過長無法點擊者必須縮網址

: https://technews.tw/2019/12/13/tsmc-5nm-process/

: 2.原文內容:

: 台積電 5 奈米製程測試良率超過 8 成,電晶體密度較 7 奈米提升 84%

: 根據外媒報導,日前在國際電子元件會議(International Electron Devices Meeting,

: IEDM)大會上,晶圓代工龍頭台積電官方接露了 5 奈米製程的最新進展。而根據公布的

: 資料顯示,5 奈米製程將會是台積電的再一個重要製成節點,其中將分為 N5、N5P 兩個

: 版本。N5 相較於當前 N7 的 7 奈米製程性能要再提升 15%、功耗降低 30%。N5P 則將

: 在 N5 的基礎上再將性能提升 7%、功耗降低 15%。

: 報導指出,台積電的 5 奈米將使用第五代 FinFET 電晶體技術,EUV 極紫外光刻技術也

: 提升到 10 多個光刻層,整體電晶體密度提升 84%。換句話說,以 7 奈米是每平方公厘

: 9,627 萬個電晶體計算,則 5 奈米就將是每平方公里有 1.771 億個電晶體。

: 同時,台積電強調,目前 5 奈米製程正在進行風險試產階段,而測試晶片的良率平均已

: 達 80%,最高良率可超過 90%,只是,相對來說這些測試晶片的架構相對簡單,要真的生

: 產行動或個人電腦處理器晶片上,目前良率可能還有些差距。不過,台積電目前並沒有公

: 開正式數據。

: 另外,台積電還公布了 5 奈米製程下的 CPU 和 GPU 晶片的電壓、頻率相對關係。目前

: CPU 通過測試的最低值是 0.7V/1.5GHz,最高可以做到 1.2V/3.25GHz,而 GPU 方面則是

: 最低 0.65V/0.66GHz,而最高則是達到 1.2V/1.43GHz。這些公布的結果都是初期的報告

: ,未來正式投產之後,後續將還會提升。

: 根據先前相關外資所進行的預估,台積電的 5 奈米製程將在 2020 年上半年,甚至最快

: 在 2020 年第 1 季末就會投入大規模量產,相關晶片產品將在 2020 年晚些時候陸續登

: 場。而包括蘋果 A14、華為海思麒麟系列新一代處理器,以及 AMD Zen4 架構第四代銳

: 龍 (Ryzen) 個人電腦處理器都將會採用。而初期的產能規劃每月 4.5 萬片,而未來將逐

: 步拉高到 8 萬片的數字,只是初期的產能將可能由蘋果吃下 70%,其餘的就由華為海思

: 包下。

: 3.心得/評論:

: ※必需填寫滿20字

: 良率有到80%甚至90%!這實在是驚人 然後初期產能由蘋果吃下70%海思30%

: 2021也規劃3奈米 看來在製程這方面 台積電還是後續看好!尤其是在5G以及

: 物聯網的加持下 營收可望再往上攀升!

--

這篇文章有示意圖

https://images.anandtech.com/doci/15219/17.92%20wafer.png

這個是八成的晶圓

可以看到每個晶片都很小

只有 17.92 mm^2

如果把那些failed 的晶片想成defect

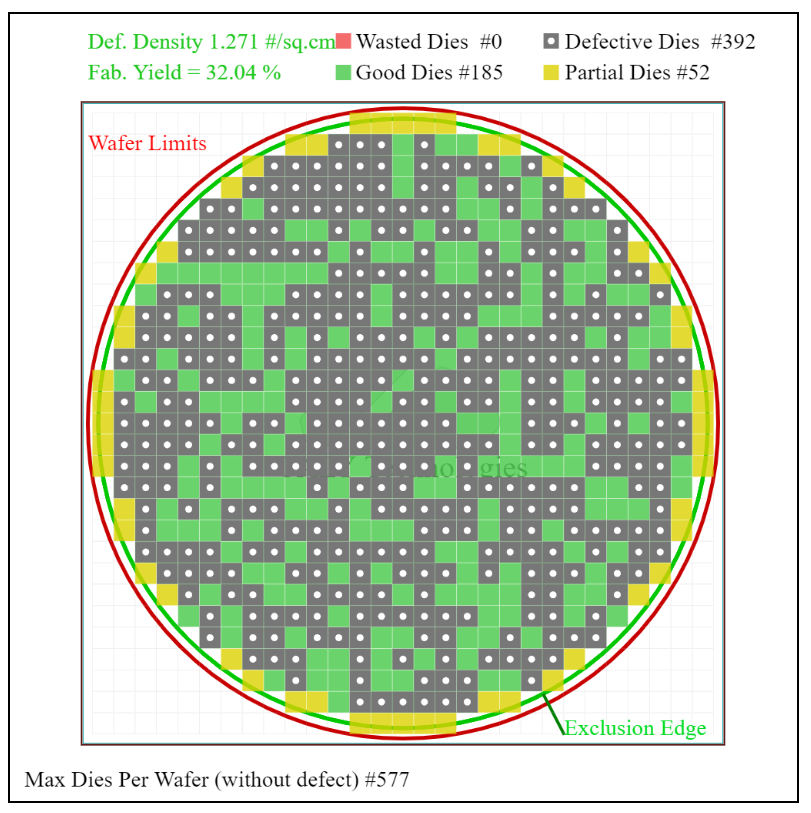

然後現在把晶片放大六倍

到100 mm^2 (相當於蘋果處理器的大小)

只要晶片有包含那個defect就算失敗的話

那良率就變成這樣:

https://images.anandtech.com/doci/15219/100%20wafer.png

良率直接從8成掉到32%

所以以這個良率來看要生產還是不太行的

※ 引述《dragonjj (簡簡單單的傷過 就不算白)》之銘言:

: -------------------------------發文提醒----------------------------------

: 1.發文前請先詳閱[新聞]分類發文規範,未依規範發文將受處份。

: 2.連結過長請善用 https://goo.gl/ 縮網址,連結能不能點擊者板規1-2-2處份。

: 3.心得/評論請盡量充實,心得過短或濫竽充數將會以1-2-3&一行文規範水桶處份。

: ---------------------------按ctrl+y可刪除以上內容。----------------------

: 1.原文連結:

: ※過長無法點擊者必須縮網址

: https://technews.tw/2019/12/13/tsmc-5nm-process/

: 2.原文內容:

: 台積電 5 奈米製程測試良率超過 8 成,電晶體密度較 7 奈米提升 84%

: 根據外媒報導,日前在國際電子元件會議(International Electron Devices Meeting,

: IEDM)大會上,晶圓代工龍頭台積電官方接露了 5 奈米製程的最新進展。而根據公布的

: 資料顯示,5 奈米製程將會是台積電的再一個重要製成節點,其中將分為 N5、N5P 兩個

: 版本。N5 相較於當前 N7 的 7 奈米製程性能要再提升 15%、功耗降低 30%。N5P 則將

: 在 N5 的基礎上再將性能提升 7%、功耗降低 15%。

: 報導指出,台積電的 5 奈米將使用第五代 FinFET 電晶體技術,EUV 極紫外光刻技術也

: 提升到 10 多個光刻層,整體電晶體密度提升 84%。換句話說,以 7 奈米是每平方公厘

: 9,627 萬個電晶體計算,則 5 奈米就將是每平方公里有 1.771 億個電晶體。

: 同時,台積電強調,目前 5 奈米製程正在進行風險試產階段,而測試晶片的良率平均已

: 達 80%,最高良率可超過 90%,只是,相對來說這些測試晶片的架構相對簡單,要真的生

: 產行動或個人電腦處理器晶片上,目前良率可能還有些差距。不過,台積電目前並沒有公

: 開正式數據。

: 另外,台積電還公布了 5 奈米製程下的 CPU 和 GPU 晶片的電壓、頻率相對關係。目前

: CPU 通過測試的最低值是 0.7V/1.5GHz,最高可以做到 1.2V/3.25GHz,而 GPU 方面則是

: 最低 0.65V/0.66GHz,而最高則是達到 1.2V/1.43GHz。這些公布的結果都是初期的報告

: ,未來正式投產之後,後續將還會提升。

: 根據先前相關外資所進行的預估,台積電的 5 奈米製程將在 2020 年上半年,甚至最快

: 在 2020 年第 1 季末就會投入大規模量產,相關晶片產品將在 2020 年晚些時候陸續登

: 場。而包括蘋果 A14、華為海思麒麟系列新一代處理器,以及 AMD Zen4 架構第四代銳

: 龍 (Ryzen) 個人電腦處理器都將會採用。而初期的產能規劃每月 4.5 萬片,而未來將逐

: 步拉高到 8 萬片的數字,只是初期的產能將可能由蘋果吃下 70%,其餘的就由華為海思

: 包下。

: 3.心得/評論:

: ※必需填寫滿20字

: 良率有到80%甚至90%!這實在是驚人 然後初期產能由蘋果吃下70%海思30%

: 2021也規劃3奈米 看來在製程這方面 台積電還是後續看好!尤其是在5G以及

: 物聯網的加持下 營收可望再往上攀升!

--

All Comments